摘要

关键词

- 金属氧化物半导体场效应晶体管 (Metal-Oxide-Semiconductor Field-Effect Transistor)

- 互补金属氧化物半导体技术 (CMOS technology)

- 亚10纳米晶体管 (sub-10-nanometre transistors)

- 晶体管缩放挑战 (Transistor Scaling Challenges)

- 后摩尔晶体管 (Beyond-MOSFET Transistors)

研究背景

MOSFET作为互补金属氧化物半导体(CMOS)技术的核心元件,在过去六十年推动了信息技术的蓬勃发展。然而,随着器件尺寸进入亚10纳米节点,其缩放面临着短沟道效应、电容寄生效应、泄漏电流等一系列问题。本文旨在通过回顾当前和未来CMOS技术的挑战,分析最具潜力的技术路径,并为研究者提供集中与高效的研究方向。

关键点

- 亚10纳米MOSFET的关键技术分析

- 新材料与器件架构对缩放的影响

- 多门结构晶体管及纳米线技术

- 碳纳米管和二维材料在未来晶体管中的应用潜力

- 后摩尔晶体管的创新方向

研究内容

以下内容重点介绍了近年来晶体管发展的重要进展:

- 高介电常数金属栅(HKMG)技术:通过采用高k材料解决传统MOSFET的氧化物泄漏问题,并显著提升晶体管性能。

- 鳍式场效应晶体管(FinFET):引入三维结构提高了晶体管的电流驱动能力,但其在5纳米以下的缩放面临诸多挑战。

- 纳米线与纳米片结构:垂直堆叠纳米线(VSNW)和纳米片(VSNS)晶体管通过增加有效传导表面积显著提高了性能。

- 二维材料晶体管:如MoS2、WSe2等显示出潜力,但仍需解决接触电阻和制造一致性等问题。

- 碳纳米管晶体管(SWNT):通过先进接触技术实现了高性能,但在一致性和规模化方面仍有待提升。

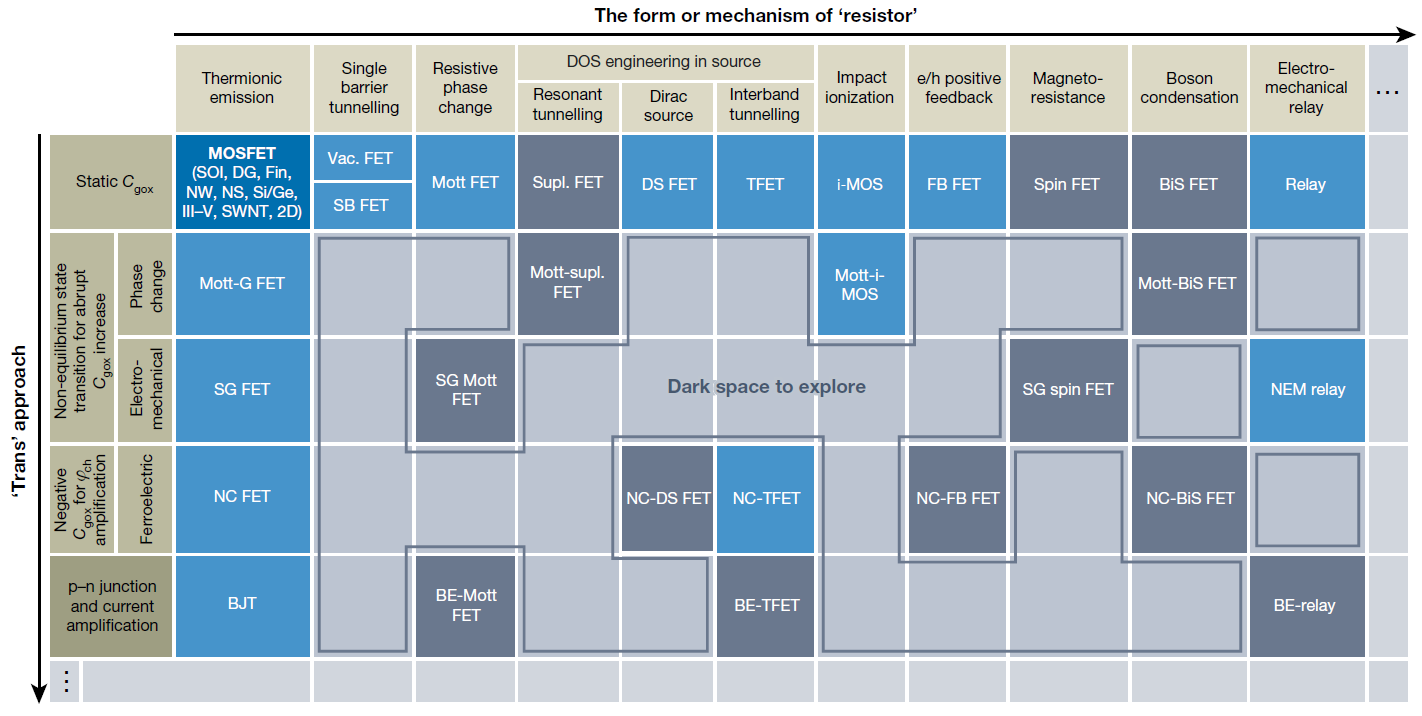

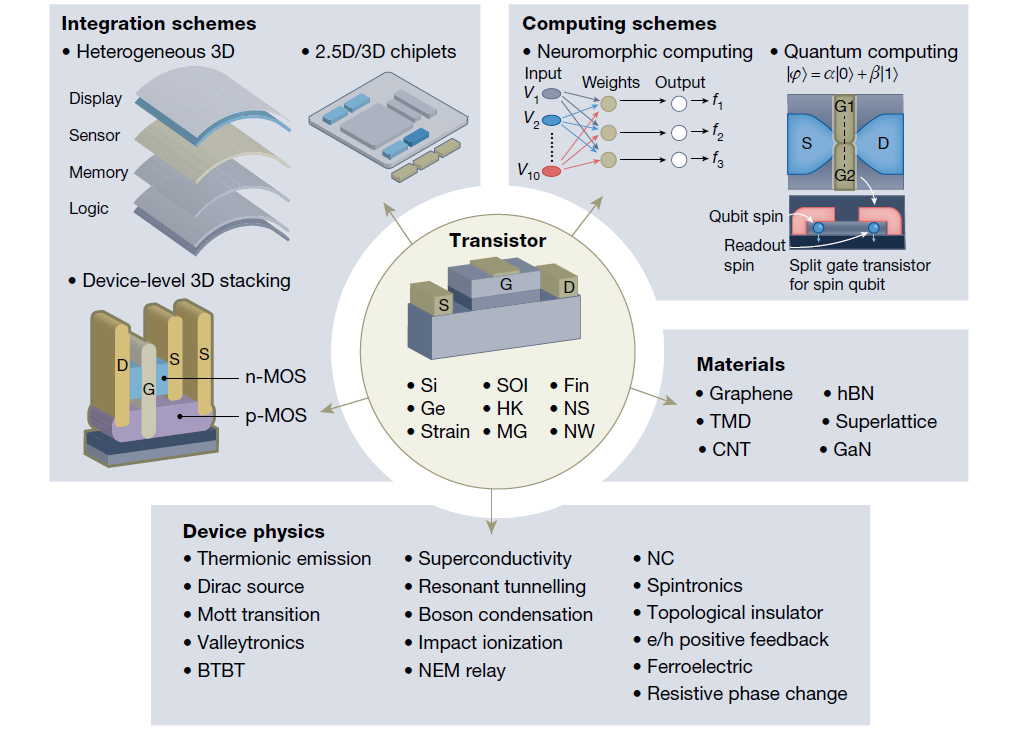

从真空管到双极型晶体管(BJT),再到金属氧化物半导体场效应晶体管(MOSFET)的主要技术变迁,均由降低功耗的需求驱动。图中展示了四种非传统场效应晶体管(FET)缩放技术,即SOI(硅绝缘体上硅技术)、应变通道、高介电常数金属栅(HKMG)和鳍式场效应晶体管(FinFET),标注了其商业化时间及对应技术节点(0.18 μm、90 nm、45 nm 和 22 nm)。注意,从22 nm节点起,技术节点逐渐小于FET的物理尺寸。Ec表示导带最小值,Ev表示价带最大值。晶体管数量数据来源:https://en.wikipedia.org/wiki/Transistor_count。

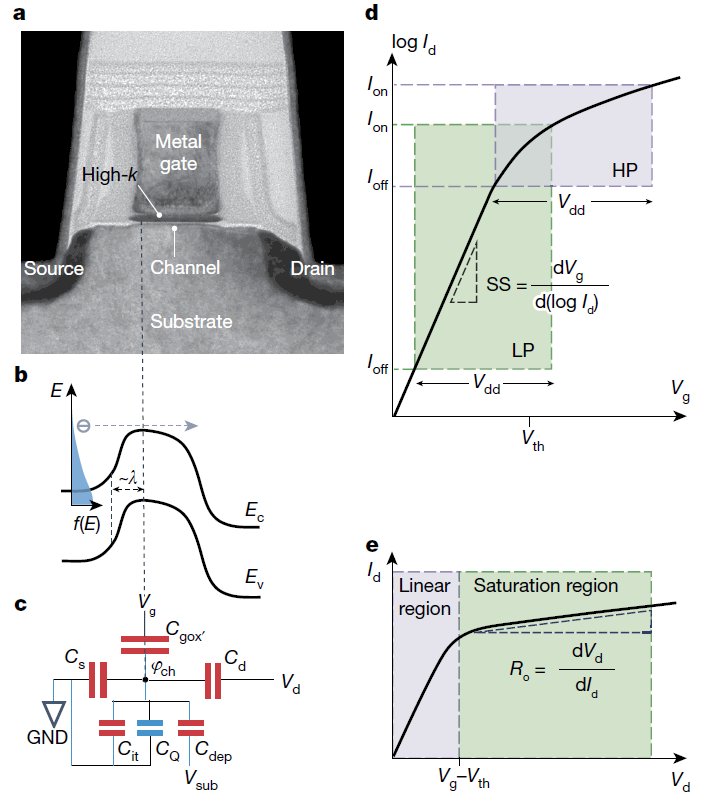

(a) 45 nm节点平面n-MOSFET的透射电子显微镜(TEM)图像,采用高k金属栅(HKMG)技术,来源:Intel公司。

(b) n型FET的能带图。Ec、Ev和f(E)分别表示导带最小值、价带最大值和费米–狄拉克分布。λ为自然长度,决定电势从源极或漏极到通道的变化距离。

(c) 示意性电容网络图,展示了接地源极条件下的电容分布。Cgox’表示修正后的栅极电容,Cs/d表示源/漏结处电容,Cdep表示耗尽引起的电容,Cit表示界面陷阱电容,CQ表示量子电容。

(d) 转移特性曲线,即Id–Vg曲线,定义了亚阈值摆幅(SS)。HP和LP应用范围标注于图中。

(e) 输出特性曲线,即Id–Vd曲线,定义了输出电阻Ro。

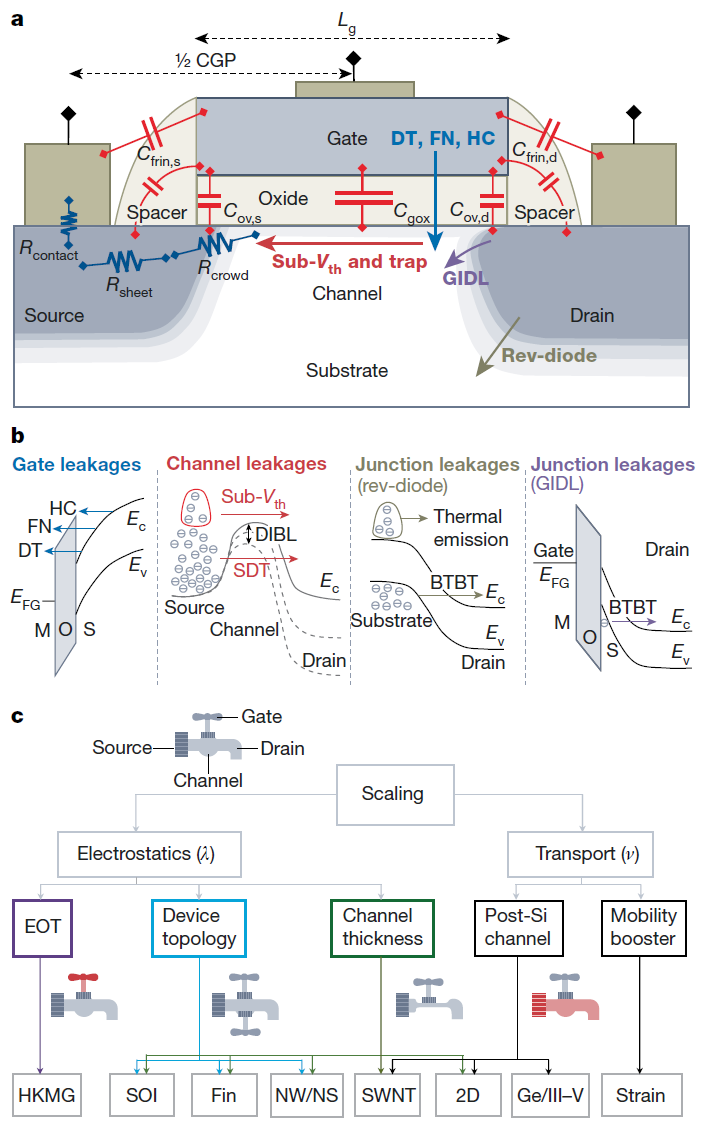

(a) 典型FET结构,展示了缩放过程中的问题,包括反向偏置二极管泄漏(Rev-diode)。

(b) MOSFET缩放过程中四种主要泄漏路径的机制示意图。EFG表示栅极的费米能级。

(c) 使用水龙头作为比喻的FET缩放场景图示,水流(电荷载流子)从源极流向漏极(通道)由栅极(旋钮)控制。不同水龙头形式表征不同的缩放场景。λ为自然长度,ν为载流子速度。

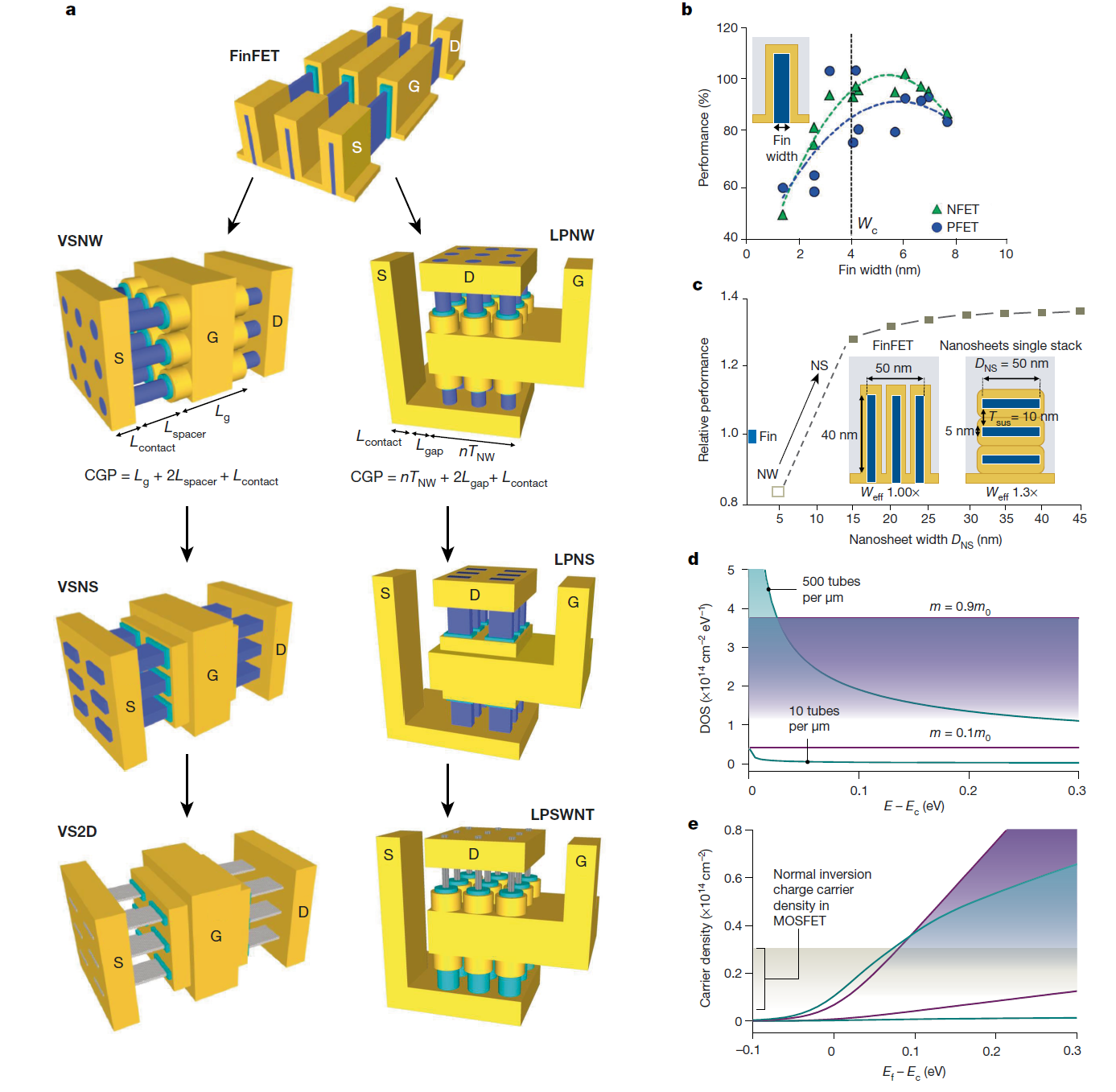

(a) 不同晶体管结构的示意图,包括FinFET、垂直堆叠纳米线(VSNW)、横向封装纳米线(LPNW)、垂直堆叠纳米片(VSNS)、横向封装纳米片(LPNS)、垂直堆叠二维材料(VS2D)和横向封装单壁碳纳米管(LPSWNT)。S/G/D分别表示源极/栅极/漏极,Lcontact/Lspacer/Lgap分别表示接触/间隔/源漏间隙长度,n为横向方向的通道数量。

(b) FinFET性能(工作频率)与鳍宽(厚度)关系,显示4 nm是最佳鳍宽。性能相对值基于14 nm技术节点。

(c) 垂直堆叠纳米片(VSNS)较FinFET在有效器件宽度(Weff)方面的优势。

(d) 单壁碳纳米管(SWNT)和二维材料(2D)在载流子密度上的比较。

(e) SWNT和二维材料的电子态密度(DOS)随能量变化曲线。

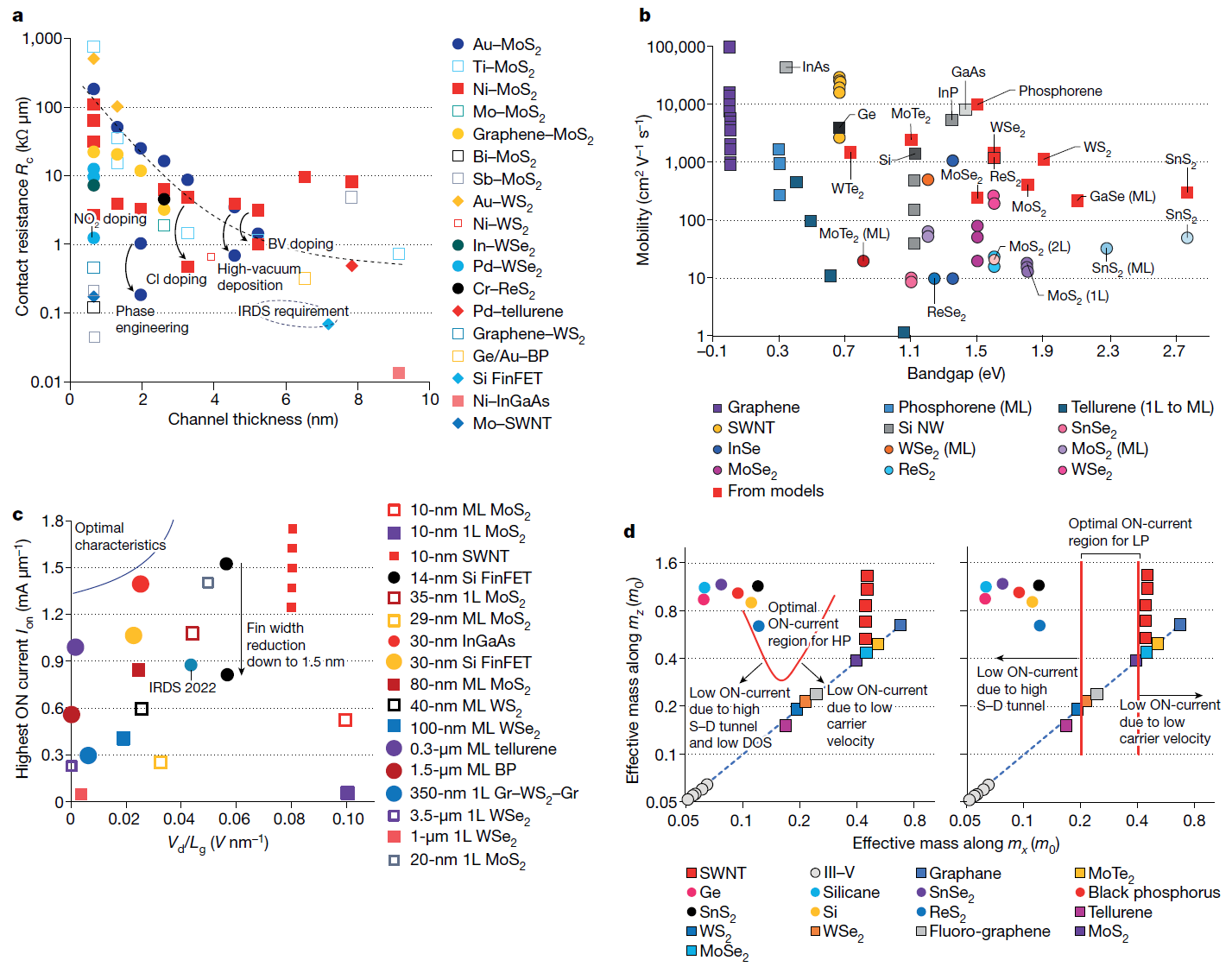

(a) 各种材料(如InGaAs、Si、SWNT、2D等)MOSFET的接触电阻与通道厚度的关系。

(b) 移动性与带隙的关系,SWNT和III–V材料显示出最高的移动性。

(c) 各种器件的最高开启电流与电场强度的关系。

(d) 基于不同材料的FET在高性能(HP)和低功耗(LP)应用中的性能映射。

(a) 展示了各种“后MOSFET”晶体管的结构示意,包括负电容晶体管(NC-FET)和相变晶体管(PC-FET)。

(b) 相变晶体管中相变材料的电导特性与电场的关系。

(c) 使用二维材料的场效应晶体管结构及其电学性能对比。

对新兴晶体管技术进行多维度评估,包括静电控制、隧穿电流、制造兼容性、开启电流(Ion)、泄漏电流(Ioff)等。结果表明,二维材料和单壁碳纳米管在可扩展性上具有显著优势。

结论与展望

晶体管的未来将继续围绕缩放与创新展开。尽管当前技术面临诸多挑战,新材料和新架构的探索将为超越摩尔定律提供新的动力。未来的晶体管不仅在尺寸上突破限制,还将在能效与计算模式上带来革命性变化。