摘要

关键词

- 二维晶体管(2D transistors)

- 铟硒(Indium Selenide, InSe)

- 超短通道效应(Short-channel effects)

- 俄欧姆接触(Ohmic contact)

- 高热速度(High thermal velocity)

- 亚纳米工艺(Sub-nanometer technology)

- 低功耗电子器件(Low-power electronics)

研究背景

近年来,随着硅基晶体管在12 nm以下的微缩技术接近物理极限,二维材料因其原子级厚度被广泛研究为未来电子器件的候选材料。然而,现有的二维晶体管性能尚未超越硅晶体管,主要挑战包括金属接触的肖特基势垒和二维材料与介电层界面的质量等。论文选用高热速度和小尺寸效应显著的InSe作为通道材料,通过先进的掺杂和加工技术,探索二维材料的极限潜能,为未来超低功耗电子器件设计提供了重要的技术突破。

创新点

- 提出钇掺杂诱导相变方法,显著降低二维材料的接触电阻。

- 实现10 nm通道长度晶体管的弹道比高达83%。

- 在0.5 V供电电压下,跨导性能首次超越硅基晶体管。

- 提供一种新的二维材料加工技术,可应用于多种亚纳米电子器件。

研究内容

论文设计了一种基于InSe的双栅结构晶体管,通过钇掺杂技术有效解决了二维材料与金属电极之间的接触问题,并采用高真空和低功率等离子处理优化了器件的界面质量。在实验中,研究人员对InSe的相变掺杂特性进行了理论和实验证明,展现了其由半导体到半金属的转变。制备的器件表现出极低的接触电阻(62 Ω μm),显著降低了功耗并提高了开态电流。此外,通过先进的测量和模拟技术,展示了其在亚纳米通道长度条件下的优异电子输运特性。

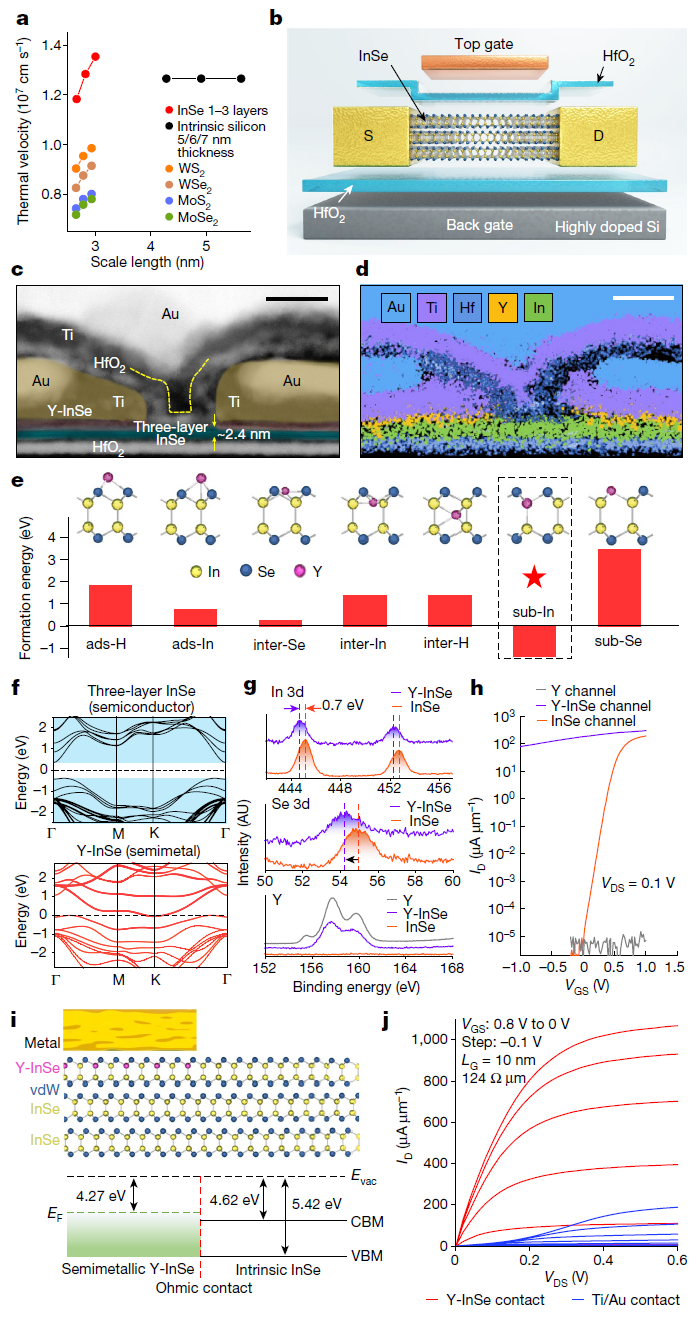

(a) 硅和典型二维半导体材料的热速度和尺度长度。

(b) 双栅InSe FET的示意图。

(c) InSe FET的透射电子显微镜图像和电子能量损失光谱图,显示双栅结构的横截面;顶部栅长约5 nm,底部栅长约10 nm,沟道长约10 nm,InSe厚度约2.4 nm,HfO2厚度约2.6 nm。比例尺:10 nm。

(d) 计算的Y-InSe系统中可能掺杂或吸附构型的形成能。金色、蓝色和紫色球分别代表In、Se和Y原子。吸附情况:Y原子吸附在InSe表面中空位点(ads-H)和In原子顶部(ads-In)。掺杂情况:Y原子分别嵌入在Se原子间(inter-Se)、In原子间(inter-In)、InSe原子间(inter-H);Y原子替代In原子(sub-In)和Se原子(sub-Se)。

(e) 三层InSe和通过钇掺杂诱导的相变接触区域(在InSe顶层中以替代方式掺杂Y原子)的计算能带结构。

(f) 与独立InSe相比,Y-InSe XPS谱图的偏移(所有C 1s峰位于284.8 eV)。AU,任意单位。

(g) 两种弹道型器件的转移特性在VDS=0.1 V,包括Y-InSe通道(紫色曲线)、纯InSe通道(橙色曲线),以及1 nm厚Y通道(灰色曲线)。

(h) 纯半导体InSe与金属化Y-InSe的带阶对齐示意图。CBM,导带最小值;VBM,价带最大值;vdW,范德华相互作用。

(i) 使用Y掺杂诱导相变接触的典型10 nm弹道型InSe FET和直接使用传统Ti/Au接触的典型10 nm InSe FET的输出特性。使用Y掺杂诱导相变接触的弹道型InSe FET的总电阻约为124 Ω μm。

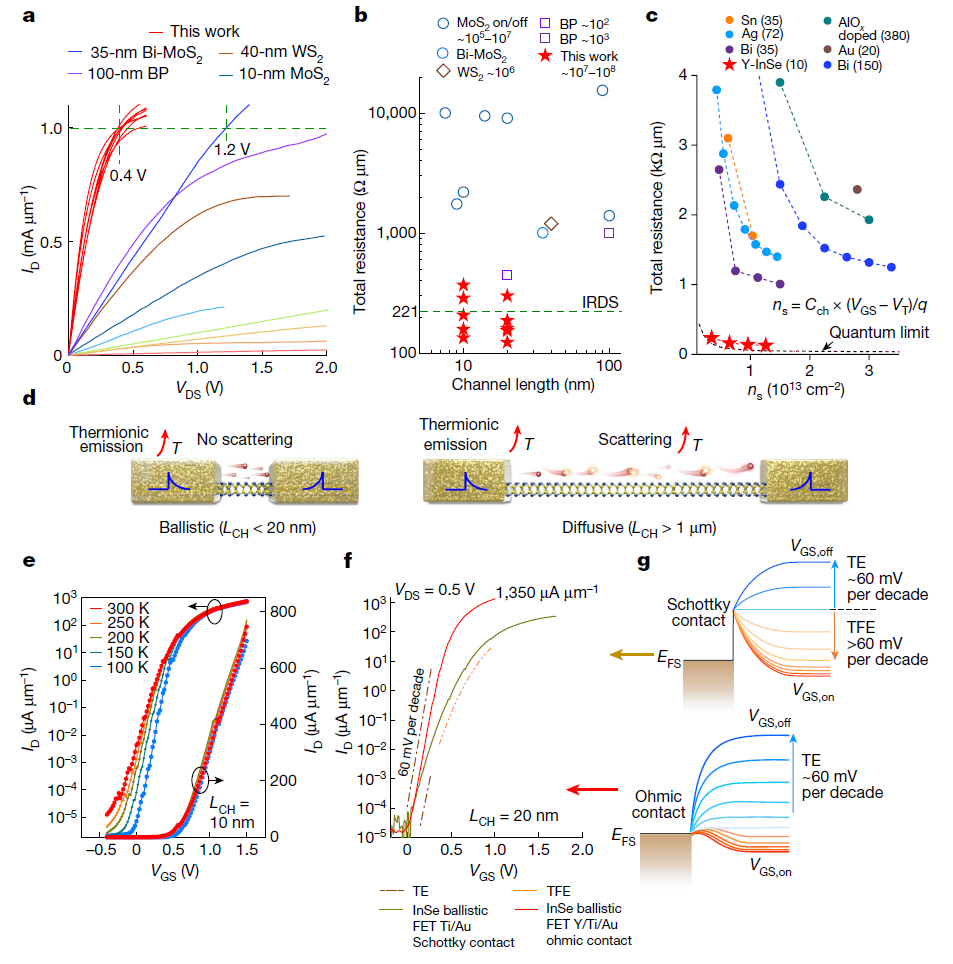

(a, b) 我们的弹道型二维InSe FET与其他二维短沟道FET的饱和输出特性(最大栅压)和总电阻对比。

(c) 几个典型研究中总电阻与载流子密度ns的对比。红星表示我们代表性10 nm沟道长度弹道型InSe FET的总电阻,虚线是使用Landauer公式计算的InSe FET理论极限。括号中的数字是沟道长度(nm)。

(d) 晶体管中与温度相关的扩散和弹道传输模式的示意图。

(e) 我们典型10 nm弹道型二维InSe FET在300 K至100 K范围内不同温度下的转移特性。

(f) 我们的弹道型二维InSe FET(Y/Ti/Au,红色)和一个弹道型二维InSe FET(普通Schottky接触Ti/Au,黄色)的典型转移特性。Ti/Au接触器件(黄色)在转移特性亚阈值区域似乎有两个部分,分别对应热发射(TE)和热场发射(TFE),这与先前报告的40 nm WS2 FET一致。相比之下,我们的欧姆接触InSe FET(红色)在整个亚阈值区域仅表现出单一热发射过程。

(g) 与肖特基接触和欧姆接触相关的带结构示意图。

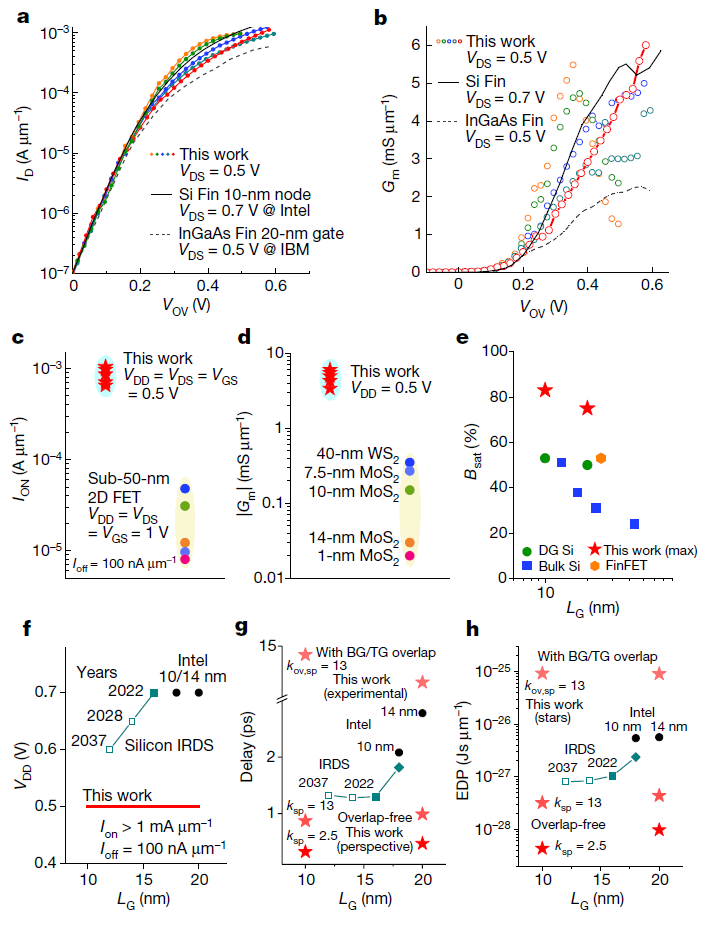

(a) 五种典型弹道型二维InSe FET(彩色点)、10 nm节点硅FinFET(Intel,实线)和20 nm栅InGaAs FinFET(IBM,虚线)的转移特性对比。

(b) (a)中五种典型弹道型二维InSe FET、10 nm节点硅FinFET(Intel,实线)和InGaAs FinFET(IBM,虚线)的跨导对比。

(c, d) 弹道型二维InSe FET在VDD=0.5 V条件下和其他二维FET在VDD=1 V条件下的开启电流和跨导峰值对比。

(e) 我们的InSe FET与硅MOS FET的弹道比基准,包括体硅FET、FinFET和双栅硅FET。

(f-h) 我们的弹道型二维InSe FET与硅FET的VDD、栅延迟和EDP(带寄生电容)的缩放趋势对比。

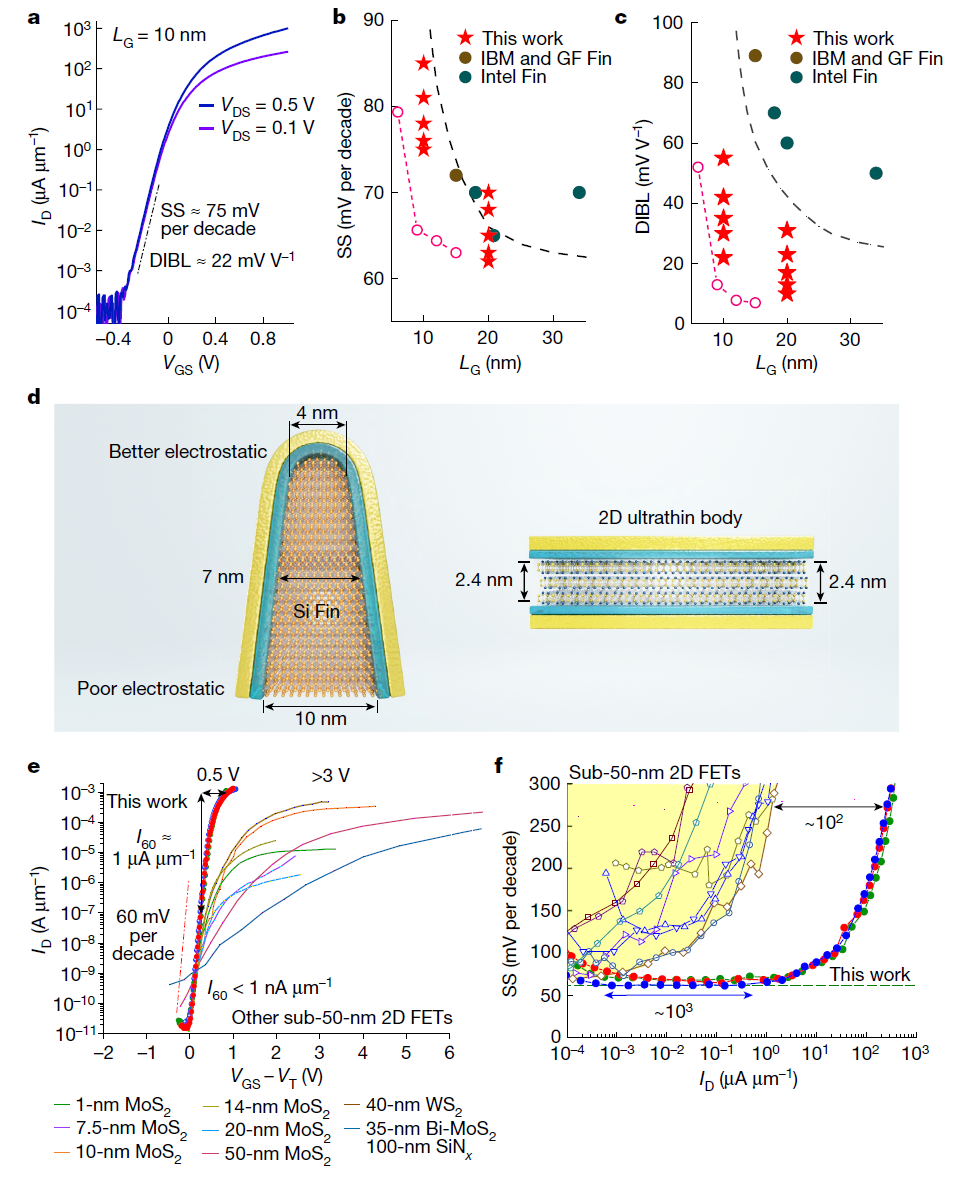

(a) 典型二维InSe FET在VDS=0.1 V(紫色)和VDS=0.5 V(蓝色)条件下、10 nm栅长度下的转移特性。

(b, c) SS和DIBL的缩放趋势。红星表示我们10 nm栅长和20 nm栅长弹道型InSe FET的结果。蓝绿色点表示Intel的10 nm节点、14 nm节点和22 nm节点FinFET的结果。棕色点表示GF和IBM联合开发的7 nm节点FinFET的结果。虚线表示单层二维FET和硅FinFET的理论计算性能。

(d) 典型10 nm节点硅FinFET和二维FET的横截面示意图。

(e) 三种20 nm栅长度弹道型二维InSe FET与报告的最佳开关性能亚50 nm二维FET的典型转移特性对比。

(f) 我们的弹道型二维InSe FET与其他亚50 nm短沟道二维FET的SS对比。

结论与展望

研究证实了二维晶体管的实际性能首次接近理论预测值,在未来亚纳米节点技术中具备挑战硅基技术的潜力。后续研究可针对InSe单层薄膜的湿度稳定性进行优化,同时探索更多维度的纳米加工和集成技术。

论文直达

原文标题:Ballistic two-dimensional InSe transistors

Nature 2023, 616, 470–475.

点击以下链接阅读原文: